ALU_Asrc ALU_Bsrc MemtoReg这三个信号对应三个多路选择器(mux), 如图中蓝色的单元所示. 它们的功能是有多个输入, 根据信号的状态选择其中一个作为输出

ALUop MemOp这两个信号会被传递给 ALU 控制单元 和 存储器控制单元, 会交给控制单元去处理, 类似 ALU 中的加减乘除等运算, Mem 中的 1/2/4字节读写的选择

RegWrite MemRead MemWrite这三个信号仅有 0 和 1 两个状态, 类似于开关

PCsrc 并没有在图中画出来, 这个稍微有点复杂, 后文结合跳转指令再提

根据这些控制信号可以得出系统在给定指令下的一个周期内所需要做的具体操作, 应该选择哪一个作为输入, 是否应该写, 是否应该读, ALU 做何种计算等等. 这时候我们就可以回答第一个问题 "其他信息(others)指的是什么?", 或者与此等价的问题 "每一阶段的 IR 都保留了哪些值?"

long __vdso_getcpu(unsigned *cpu, unsigned *node, struct getcpu_cache *unused)

{

vdso_read_cpunode(cpu, node);

return 0;

}

long getcpu(unsigned *cpu, unsigned *node, struct getcpu_cache *tcache)

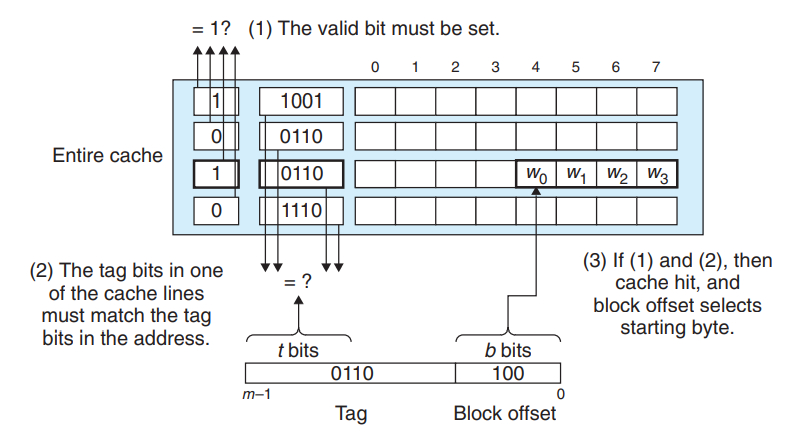

__attribute__((weak, alias("__vdso_getcpu")));因为高速缓存电路必须并行的遍历所有行,匹配所有标记位,所以构造一个又大又快的相联高速缓存困难且昂贵,因此全相联高速缓存指适合做小的高速缓存, 例如虚拟内存中的快表TLB

地址访问

处理器在进行存储器访问时,处理器访问的地址是虚拟地址,经过MMU的转换,得到物理地址.那么查询cache组是用虚拟地址还是物理地址的Index域呢?当找到cache组时,使用虚拟地址,还是物理地址的Tag域来匹配cache line呢?

有如下三种策略:

- VIVT(Virtual Index Virtual Tag):使用虚拟地址Index域和虚拟地址Tag域

- VIPT(Virtual Index Physical Tag):使用虚拟地址Index域和物理地址Tag域

- PIPT(Physical Index Physical Tag):使用物理地址Index域和物理地址Tag域

VIVT/VIPT/PIPT的优缺点分析:

- VIVT:多个VA可能映射到同一PA,导致多个cache line组(VA不同,index域不同,查找到的cache 组则不同)映射到同一物理地址,这种现象叫做cache alias(高速缓存别名).一旦一个VA到PA的映射关系改变,cache内容将会写回物理内存.此时,由于物理内存内容的变化需要同步到cache,就需要clean和invalidate(这两个操作结合起来就叫做flush)其余同名cache line,导致系统性能下降.

- VIPT:如果index域位于地址的bit0~bit11(因为linux kernel以4KB(12bit位宽)大小为页面进行物理内存管理),就不会引起cache alias,否则还是会引起该问题.因为对于一个页面来说,虚拟地址和物理地址的低12bit是完全一样的,如果index域位于bit0~bit11,此时VIPT等价于PIPT.

- PIPT:就不会存在cache alias问题,但是结构更复杂.ARM Cortex-A系列处理器使用的是PIPT方式.